Rowan University Rowan Digital Works

**Open Educational Resources**

7-24-2018

## **Computer Organization with MIPS**

Seth D. Bergmann Rowan University

Follow this and additional works at: https://rdw.rowan.edu/oer

Part of the Computer Sciences Commons

DOI: 10.31986/issn.2689-0690\_rdw.oer.1008

Let us know how access to this document benefits you - share your thoughts on our feedback form.

## **Recommended Citation**

Bergmann, Seth D., "Computer Organization with MIPS" (2018). *Open Educational Resources*. 9. https://rdw.rowan.edu/oer/9

This Book is brought to you for free and open access by Rowan Digital Works. It has been accepted for inclusion in Open Educational Resources by an authorized administrator of Rowan Digital Works.

# Computer Organization with MIPS

Seth D. Bergmann

June 2, 2023

# Preface

This book is intended to be used for a first course in computer organization, or computer architecture. It assumes that all digital components can be constructed from fundamental logic gates.

The book begins with number representation schemes and assembly language for the MIPS architecture, including assembler directives, pseudo-operations, and floating point instructions. It then describes the machine language instruction formats, and shows the student how to translate an assembly language program to machine language.

This is followed by a chapter which describes how to construct an assembler for MIPS. This chapter may be omitted without loss of continuity.

There is then an introduction to boolean algebra and digital logic, followed by a design of the MIPS datapath. This is followed by a description of the memory hierarchy, including cache memory, RAM, and virtual memory.

The book concludes with brief descriptions of some alternative architectures.

Each section concludes with a list of exercises (solutions are available to instructors who have adopted this text in a course).

This book is an open source book. This means that not only is the pdf version available (to potential students and teachers) for free download, but that the original (LaTeX) source files are also available (to potential authors and contributors). Based on the model of open source software, open source for textbooks is a relatively new paradigm in which many authors and contributors can cooperate to produce a high quality product, for no compensation. For details on the rationale of this new paradigm, and citations for other open source textbooks, see the journal *Publishing Research Quarterly*, Vol. 30, No. 1, March 2014. The source materials and pdf files of this book are licensed with the Creative Commons NonCommercial license, which means that they may be freely used, copied, or modified, but not for financial gain.

The source files for this book are available at rdw.rowan.edu (search for Bergmann) and at cs.rowan.edu/~bergmann/books

#### PREFACE

# Secondary Authors

## Contributors

## **Technical Consultant**

Joshua Grochowski, Rowan University

# Contents

| Pr       | reface | 9                                                 | i  |

|----------|--------|---------------------------------------------------|----|

| 1        | Con    | nputers and Computer Programs                     | 1  |

|          | 1.1    | Hardware Components                               | 2  |

|          |        | 1.1.1 Central Processing Unit                     | 2  |

|          |        | 1.1.2 Memory                                      | 3  |

|          |        | 1.1.3 Peripheral Devices                          | 4  |

|          | 1.2    | Machine Language                                  | 6  |

|          | 1.3    | Assembly Language                                 | 6  |

|          | 1.4    | Operating System                                  | 6  |

|          | 1.5    | Programming Languages                             | 7  |

|          | 1.6    | Exercises                                         | 7  |

| <b>2</b> | Nur    | nber Systems                                      | 9  |

|          | 2.1    | Base Two - Binary                                 | 9  |

|          |        | 2.1.1 Binary Arithmetic                           | 10 |

|          |        | 2.1.2 Exercises                                   | 11 |

|          | 2.2    | Base 8 - Octal                                    | 12 |

|          |        | 2.2.1 Exercises                                   | 13 |

|          | 2.3    | Base 16 - Hexadecimal                             | 14 |

|          |        | 2.3.1 Hexadecimal Values in the MIPS Architecture | 16 |

|          |        | 2.3.2 Exercises                                   | 16 |

|          | 2.4    | Twos Complement Representation                    | 17 |

|          |        | 2.4.1 Exercises                                   | 20 |

|          | 2.5    | Powers of Two                                     | 21 |

|          |        | 2.5.1 Arithmetic With Powers of Two               | 23 |

|          |        | 2.5.2 Exercises                                   | 23 |

| 3        | Ass    | embly Language for MIPS                           | 25 |

| 0        | 3.1    | Registers and Register Names                      | 25 |

|          | 5.1    | 3.1.1 Exercises                                   | 26 |

|          | 3.2    | Assembly Language Statements                      | 26 |

|          | J      | 3.2.1 Exercises                                   | 27 |

|          | 3.3    | Arithmetic Instructions                           | 27 |

### CONTENTS

|      | 3.3.1   | Add Instruction                           | • |  | 28  |

|------|---------|-------------------------------------------|---|--|-----|

|      | 3.3.2   | Subtract Instruction                      |   |  | 29  |

|      | 3.3.3   | Examples of Add and Subtract Instructions |   |  | 29  |

|      | 3.3.4   | Set If Less Than                          | • |  | 30  |

|      | 3.3.5   | Exercises                                 |   |  | 31  |

| 3.4  | Logica  | al Instructions                           |   |  | 32  |

|      | 3.4.1   | Logical Operations                        |   |  |     |

|      | 3.4.2   | MIPS Logical Instructions                 |   |  |     |

|      | 3.4.3   | Exercises                                 |   |  |     |

| 3.5  | Shift I | Instructions                              |   |  | 39  |

|      | 3.5.1   | Logical Shift Instructions                |   |  | 39  |

|      | 3.5.2   | Arithmetic Shift Instructions             |   |  |     |

|      | 3.5.3   | Common Applications of Shift Instructions |   |  |     |

|      | 3.5.4   | Exercises                                 |   |  | 42  |

| 3.6  | Immed   | diate Instructions                        |   |  | 43  |

| 0.0  | 3.6.1   | Add, Load, Move, and PsuedoOps            |   |  | 44  |

|      | 3.6.2   | Logical Immediate Instructions            |   |  | 46  |

|      | 3.6.3   | Load Upper Immediate                      |   |  | 48  |

|      | 3.6.4   | Exercises                                 |   |  | 49  |

| 3.7  | 0.0     | ry Reference Instructions                 |   |  | 50  |

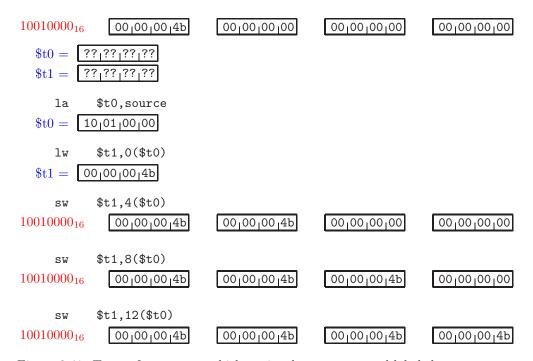

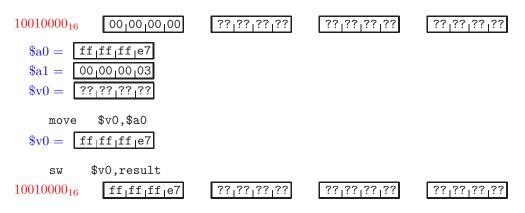

| 0.1  | 3.7.1   | Symbolic Memory Addresses                 |   |  | 51  |

|      | 3.7.2   | Non-symbolic Load and Store               |   |  | 56  |

|      | 3.7.3   | Exercises                                 |   |  | 58  |

| 3.8  | 0       | fer of Control                            |   |  |     |

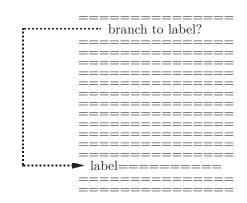

| 0.0  | 3.8.1   | Conditional Transfer of Control: Branch   |   |  |     |

|      | 3.8.2   | Unconditional Transfer of Control: Jump   |   |  |     |

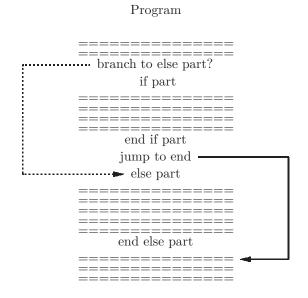

|      | 3.8.3   | Selection Structures                      |   |  |     |

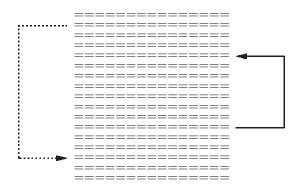

|      | 3.8.4   | Iteration Structures - Loops              |   |  |     |

|      | 3.8.5   | Exercises                                 |   |  | 71  |

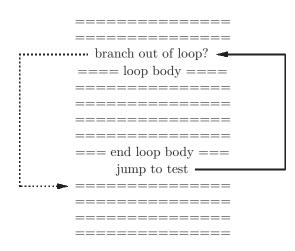

| 3.9  | Memor   | ry Arrays                                 |   |  | 73  |

|      | 3.9.1   | Exercises                                 |   |  | 74  |

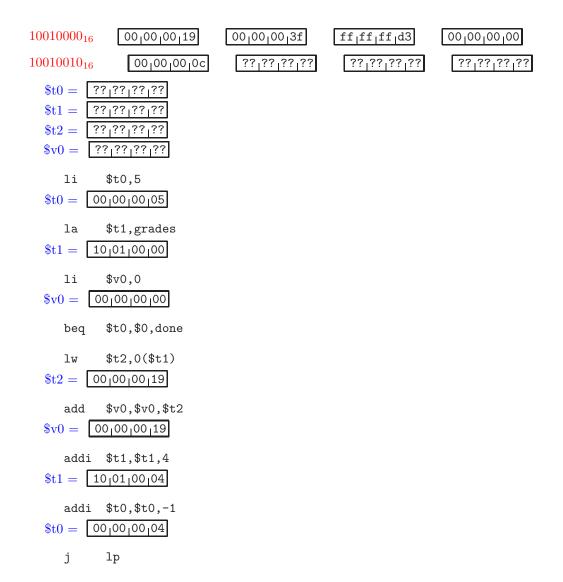

| 3.10 | Functi  | ions                                      |   |  | 77  |

|      |         | Function Calls - jal and jr               |   |  | 77  |

|      |         | Function Parameters                       |   |  | 83  |

|      |         | Register Conventions and the Call Stack   |   |  | 84  |

|      |         | Recursive Functions                       |   |  | 94  |

|      |         | Exercises                                 |   |  | 95  |

| 3.11 |         | s and String Functions                    |   |  |     |

|      |         | Initializing Memory with Strings          |   |  | 98  |

|      |         | Byte Instructions - 1bu and sb            |   |  | 99  |

|      |         | String Processing                         |   |  | 100 |

|      |         | Exercises                                 |   |  | 102 |

| 3.12 | 0       | plication of Whole Numbers                |   |  |     |

|      | -       | Multiplication with Software              |   |  |     |

|      |         | Multiplication with a MIPS Instruction    |   |  |     |

|      |         | Exercises                                 |   |  |     |

|      |         |                                           |   |  |     |

iv

|   | 3.13 | Divisio | on                                           | 113 |

|---|------|---------|----------------------------------------------|-----|

|   |      | 3.13.1  | Division Implemented in Software             | 114 |

|   |      | 3.13.2  | Division with a MIPS Instruction             | 118 |

|   |      | 3.13.3  | Exercises                                    | 119 |

|   | 3.14 | Floatin | ng Point Instructions                        | 121 |

|   |      | 3.14.1  | Floating Point Registers                     | 122 |

|   |      | 3.14.2  | Floating Point Instructions                  | 122 |

|   |      | 3.14.3  | Floating Point Data in Memory                | 124 |

|   |      | 3.14.4  | Loading and Storing Floating Point Registers | 125 |

|   |      |         | Floating Point Comparisons                   |     |

|   |      | 3.14.6  | Type conversions                             | 131 |

|   |      | 3.14.7  | Exercises                                    | 135 |

|   | 3.15 | Input,  | Output, and Other System Calls With MARS     | 138 |

|   |      |         | Normal Program Termination                   |     |

|   |      |         | Input with syscall                           |     |

|   |      |         | Output with syscall                          |     |

|   |      |         | Example for Input and Output                 |     |

|   |      |         | Exercises                                    |     |

|   |      |         |                                              |     |

| 4 | Mac  |         | anguage for MIPS                             | 144 |

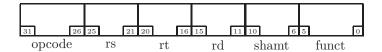

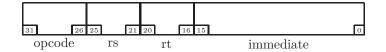

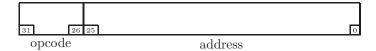

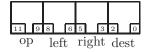

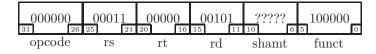

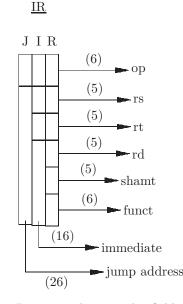

|   | 4.1  |         | ction Formats                                |     |

|   |      | 4.1.1   | Introduction to the Instruction Formats      |     |

|   |      | 4.1.2   | Exercises                                    |     |

|   | 4.2  |         | ng Binary Fields                             |     |

|   |      | 4.2.1   | Exercises                                    |     |

|   | 4.3  |         | o Operations                                 |     |

|   |      | 4.3.1   | Load Immediate                               |     |

|   |      | 4.3.2   | Move                                         |     |

|   |      | 4.3.3   | Not                                          |     |

|   |      | 4.3.4   | Load Address                                 |     |

|   |      | 4.3.5   | Other Pseudo Operations                      |     |

|   |      | 4.3.6   | Exercises                                    |     |

|   | 4.4  | R Form  | nat Instructions                             |     |

|   |      | 4.4.1   | Add and Subtract Instructions                |     |

|   |      | 4.4.2   | Logical Instructions                         |     |

|   |      | 4.4.3   | Shift Instructions                           |     |

|   |      | 4.4.4   | Multiply and Divide Instructions             |     |

|   |      | 4.4.5   | Jump Register                                | 158 |

|   |      | 4.4.6   | Exercises                                    |     |

|   | 4.5  |         | nat Instructions                             |     |

|   |      | 4.5.1   | Immediate instructions using constants       |     |

|   |      | 4.5.2   | Memory Reference Instructions                |     |

|   |      | 4.5.3   | Memory Reference - Symbolic                  |     |

|   |      | 4.5.4   | Conditional Branches                         | 166 |

|   |      | 4.5.5   | Exercises                                    |     |

|   | 4.6  | J Form  | nat Instructions                             | 172 |

### CONTENTS

|   |     | 4.6.1                                                  | Exercises                                                                    | . 174                                     |

|---|-----|--------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------|

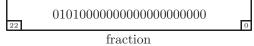

|   | 4.7 | Floati                                                 | ng Point Data Representation                                                 | . 175                                     |

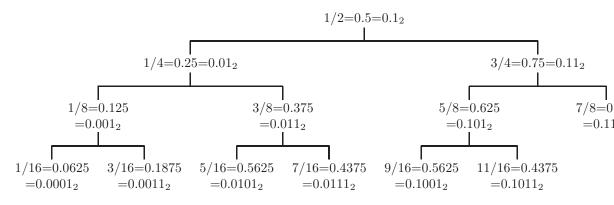

|   |     | 4.7.1                                                  | Fixed Point in Binary                                                        | . 175                                     |

|   |     | 4.7.2                                                  | IEEE 754 Floating Point Data Representation                                  | . 177                                     |

|   |     | 4.7.3                                                  | Exercises                                                                    |                                           |

|   | 4.8 | Floati                                                 | ng Point Instructions                                                        | . 179                                     |

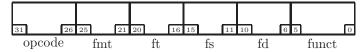

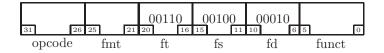

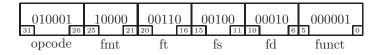

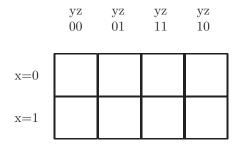

|   |     | 4.8.1                                                  | MIPS Arithmetic Floating Point Instruction Formats                           | . 180                                     |

|   |     | 4.8.2                                                  | Floating Point Memory Reference Instruction Formats                          | . 181                                     |

|   |     | 4.8.3                                                  | Floating Point Conditional Branch Instruction Formats .                      | . 182                                     |

|   |     | 4.8.4                                                  | Exercises                                                                    | . 184                                     |

| 5 | Δ٦  | AIPS 4                                                 | Assembler                                                                    | 185                                       |

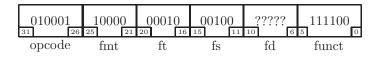

| 0 | 5.1 |                                                        | on 1 - R Format Instructions Only                                            |                                           |

|   | 0.1 | 5.1.1                                                  | Version 1a - No Symbolic Registers                                           |                                           |

|   |     | 5.1.2                                                  | Version 1b - Allow Symbolic Registers                                        |                                           |

|   |     | 5.1.2<br>5.1.3                                         | Include Directives                                                           |                                           |

|   |     | 5.1.4                                                  | Exercises                                                                    |                                           |

|   | 5.2 | -                                                      | on 2 - Include I and J Format Instructions                                   |                                           |

|   | 0.2 | 5.2.1                                                  | Version 2a - I and J Format Instructions                                     |                                           |

|   |     | 5.2.1                                                  | Version 2b - Explicit Memory Addresses                                       |                                           |

|   |     | 5.2.2                                                  | Exercises                                                                    |                                           |

|   | 5.3 |                                                        | on 3 - More Pseudo Operations                                                |                                           |

|   |     |                                                        | -                                                                            |                                           |

| 6 |     |                                                        | Algebra and Digital Logic                                                    | 213                                       |

|   | 6.1 |                                                        | ion for Boolean Functions                                                    |                                           |

|   |     | 6.1.1                                                  | Boolean Expressions                                                          |                                           |

|   |     | 6.1.2                                                  | Minimizing Boolean Expressions                                               |                                           |

|   |     | 6.1.3                                                  | Exercises                                                                    |                                           |

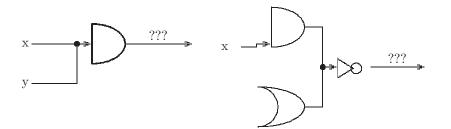

|   | 6.2 |                                                        | Logic Gates                                                                  |                                           |

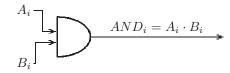

|   |     | 6.2.1                                                  | AND Gates                                                                    |                                           |

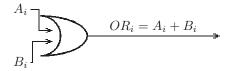

|   |     | 6.2.2                                                  | OR Gates                                                                     |                                           |

|   |     | 6.2.3                                                  | Inverters                                                                    |                                           |

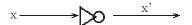

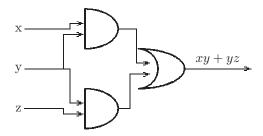

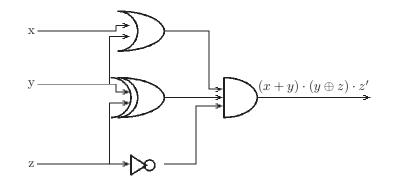

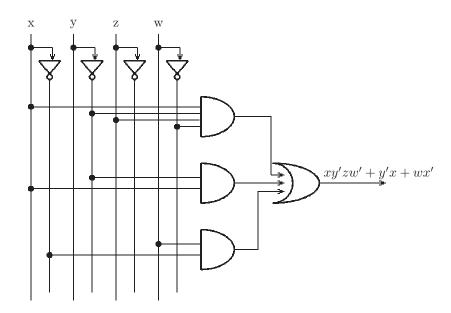

|   |     | 6.2.4                                                  | Composition of Logic Gates                                                   |                                           |

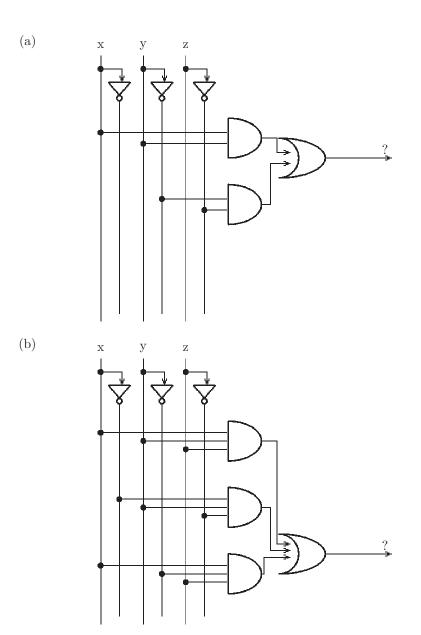

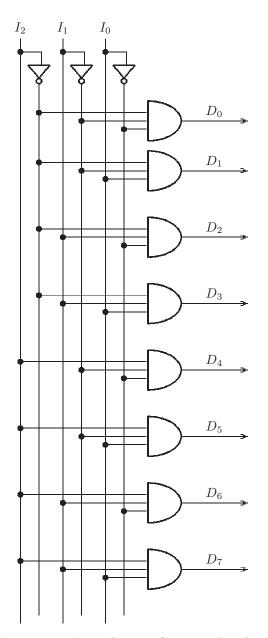

|   |     | 6.2.5                                                  | Sum of Products Logic Diagrams                                               |                                           |

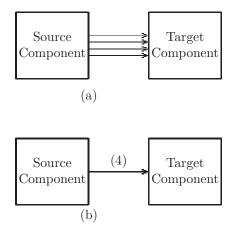

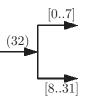

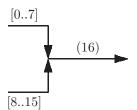

|   |     | 6.2.6                                                  | Wires and Buses                                                              |                                           |

|   | 0.0 | 6.2.7                                                  | Exercises                                                                    |                                           |

|   | 6.3 |                                                        | inational Logic Circuits and Components                                      |                                           |

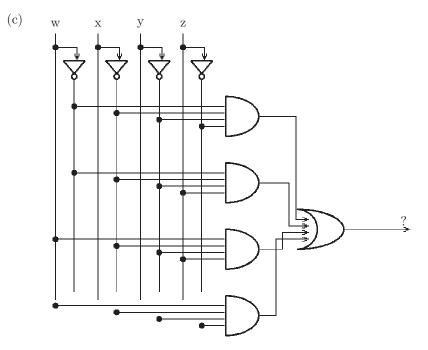

|   |     | 6.3.1                                                  | Sign Extend                                                                  |                                           |

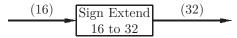

|   |     | 6.3.2                                                  | Decoders                                                                     |                                           |

|   |     | 0.0.0                                                  |                                                                              |                                           |

|   |     | 6.3.3                                                  | Encoders                                                                     |                                           |

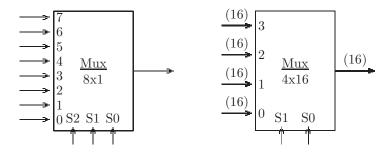

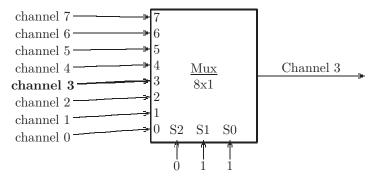

|   |     | 6.3.4                                                  | Multiplexers                                                                 | . 235                                     |

|   |     | $\begin{array}{c} 6.3.4 \\ 6.3.5 \end{array}$          | Multiplexers                                                                 | . 235<br>. 239                            |

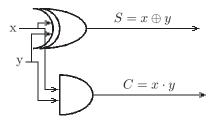

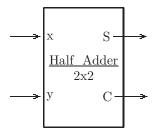

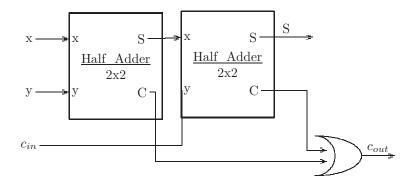

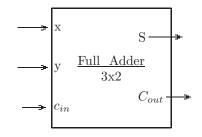

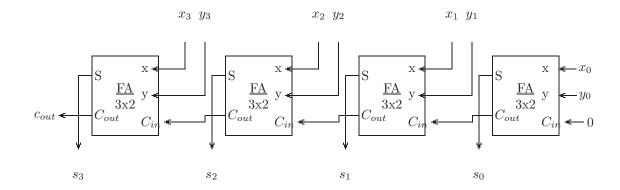

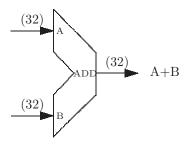

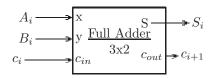

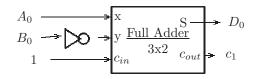

|   | 0.4 | $\begin{array}{c} 6.3.4 \\ 6.3.5 \\ 6.3.6 \end{array}$ | Multiplexers       .         Binary Adders       .         Exercises       . | . 235<br>. 239<br>. 244                   |

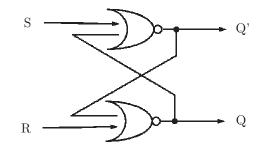

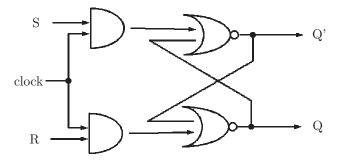

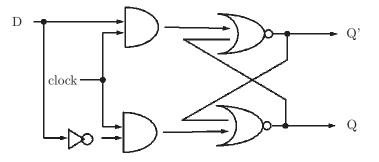

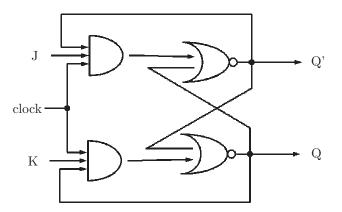

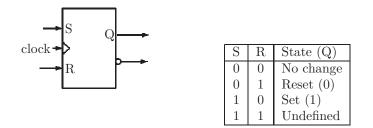

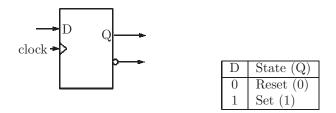

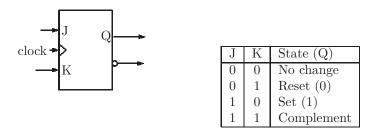

|   | 6.4 | 6.3.4<br>6.3.5<br>6.3.6<br>Sequer                      | Multiplexers                                                                 | . 235<br>. 239<br>. 244<br>. 245          |

|   | 6.4 | $\begin{array}{c} 6.3.4 \\ 6.3.5 \\ 6.3.6 \end{array}$ | Multiplexers       .         Binary Adders       .         Exercises       . | . 235<br>. 239<br>. 244<br>. 245<br>. 246 |

vi

|   |     | 6.4.3  | JK Flip-Flops                                             | . 248           |

|---|-----|--------|-----------------------------------------------------------|-----------------|

|   |     | 6.4.4  | Block Diagrams and Function Tables for Flip-Flops         | . 249           |

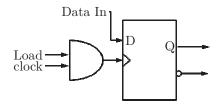

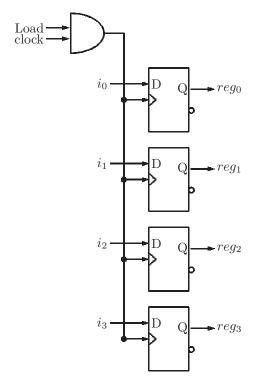

|   |     | 6.4.5  | Registers                                                 | . 249           |

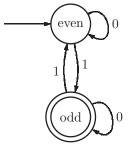

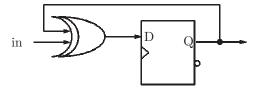

|   |     | 6.4.6  | State Machines                                            | . 251           |

|   |     | 6.4.7  | Exercises                                                 | . 254           |

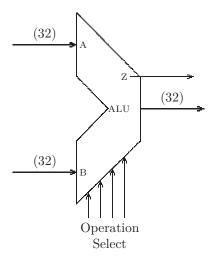

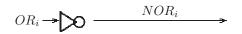

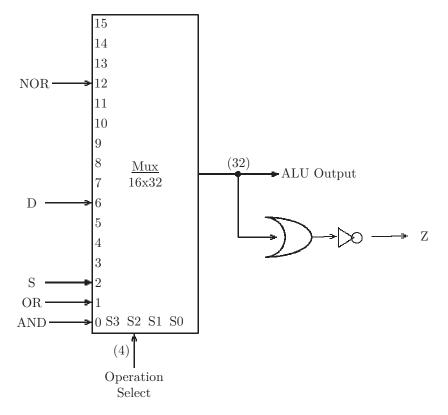

|   | 6.5 | An Ar  | ithmetic and Logic Unit - ALU                             | . 255           |

|   |     | 6.5.1  | Exercises                                                 |                 |

|   | 6.6 | Const  | ruction of the ALU                                        | . 257           |

|   |     | 6.6.1  | ALU function AND: 0000                                    | . 257           |

|   |     | 6.6.2  | ALU function OR: 0001                                     | . 258           |

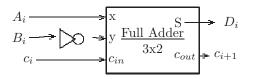

|   |     | 6.6.3  | ALU function Add: 0010                                    | . 258           |

|   |     | 6.6.4  | ALU function Subtract: 0110                               | . 258           |

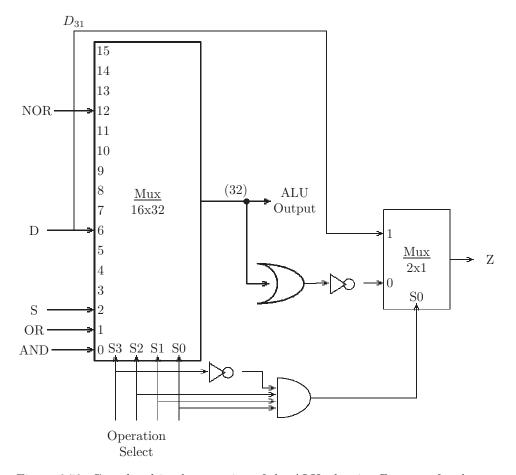

|   |     | 6.6.5  | ALU function NOR: 1100                                    | . 260           |

|   |     | 6.6.6  | ALU: Putting it all together                              | . 260           |

|   |     | 6.6.7  | Exercises                                                 |                 |

|   |     |        |                                                           | -               |

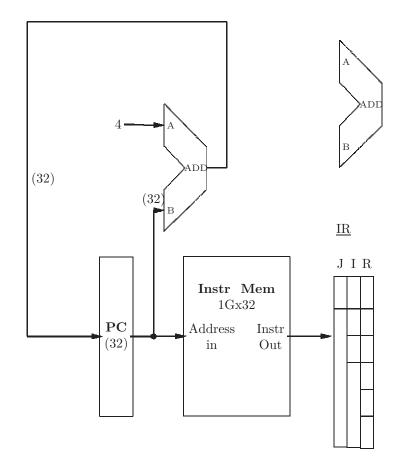

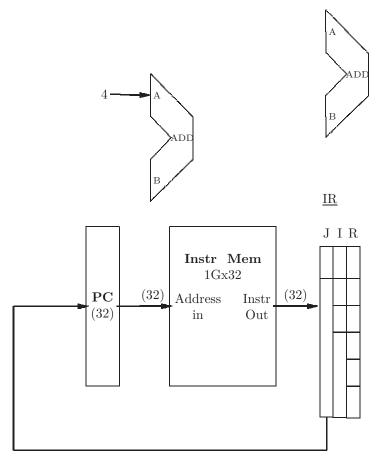

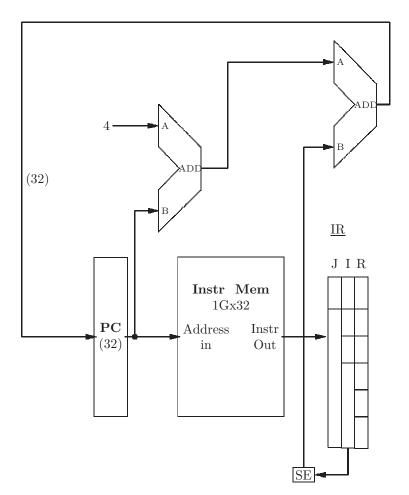

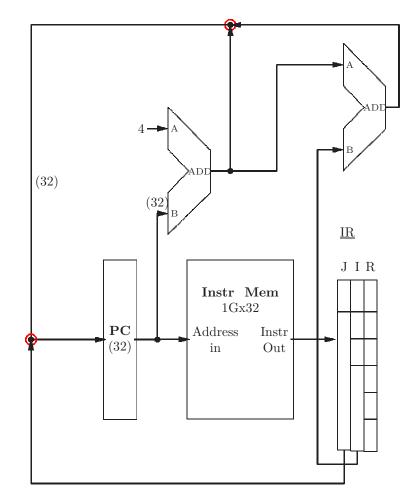

| 7 | MI  | PS Dat | tapath                                                    | 264             |

|   | 7.1 | Storag | ge Components                                             | . 264           |

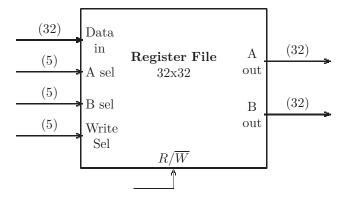

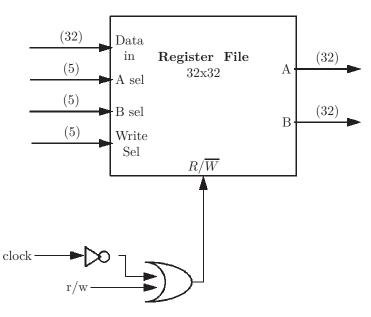

|   |     | 7.1.1  | The Register File                                         | . 264           |

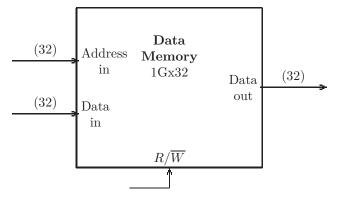

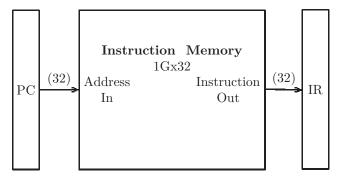

|   |     | 7.1.2  | Data Memory and Instruction Memory                        | . 265           |

|   |     | 7.1.3  | Exercises                                                 | . 268           |

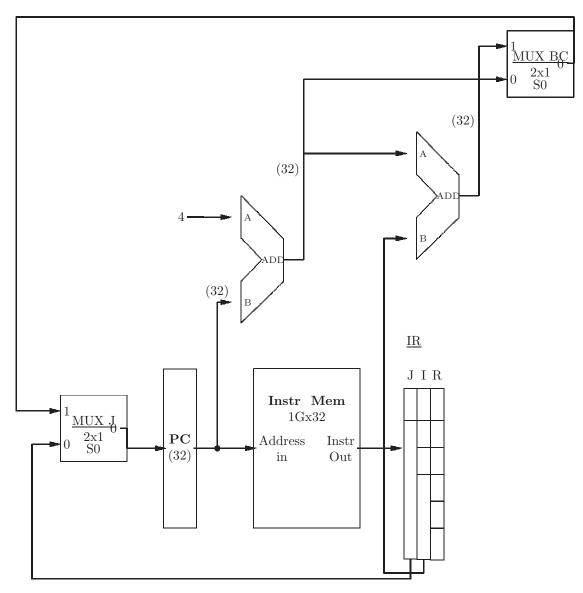

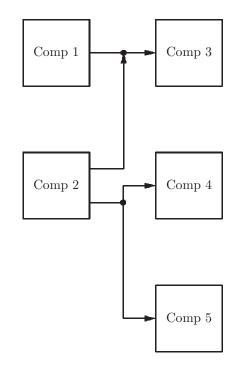

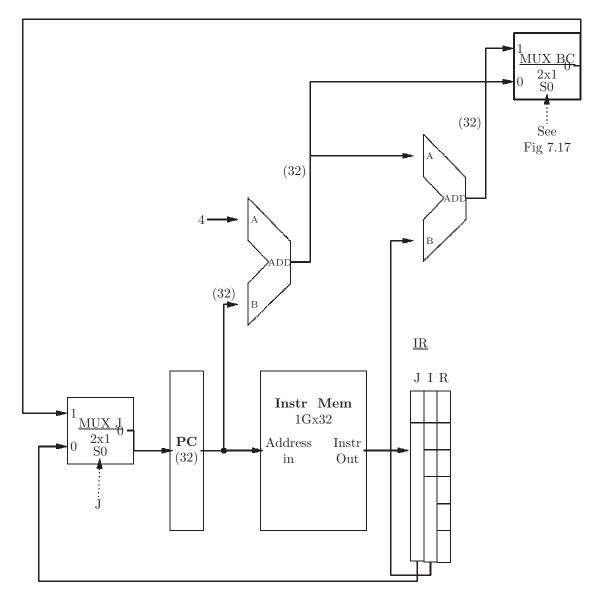

|   | 7.2 | Design | of the Datapath                                           | . 269           |

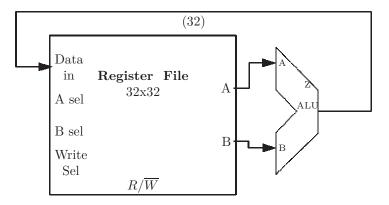

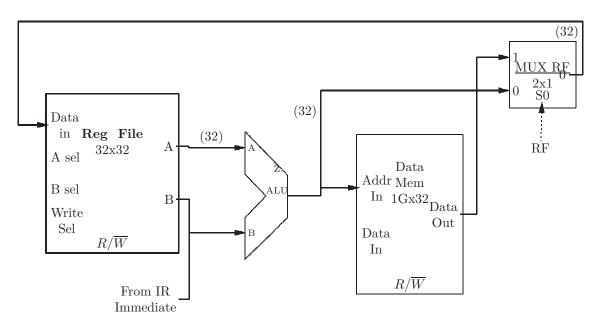

|   |     | 7.2.1  | Register File and ALU                                     | . 271           |

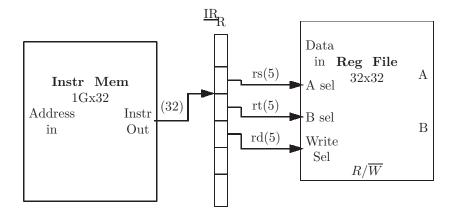

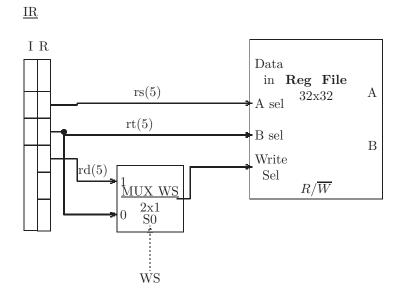

|   |     | 7.2.2  | Instruction Memory, Instruction Register, and Register F  | ile271          |

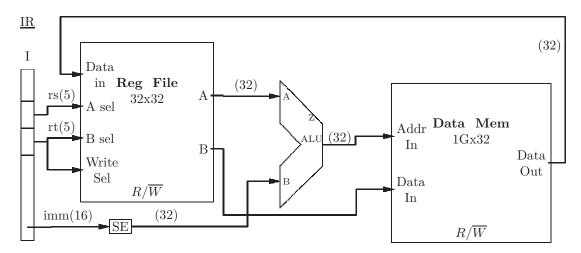

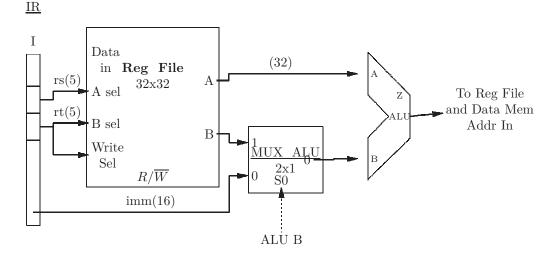

|   |     | 7.2.3  | Instruction Register, Register File, and Data Memory, for | : Load/Store272 |

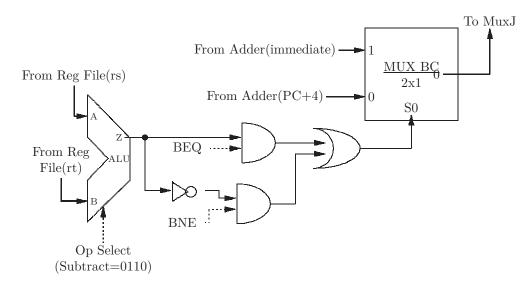

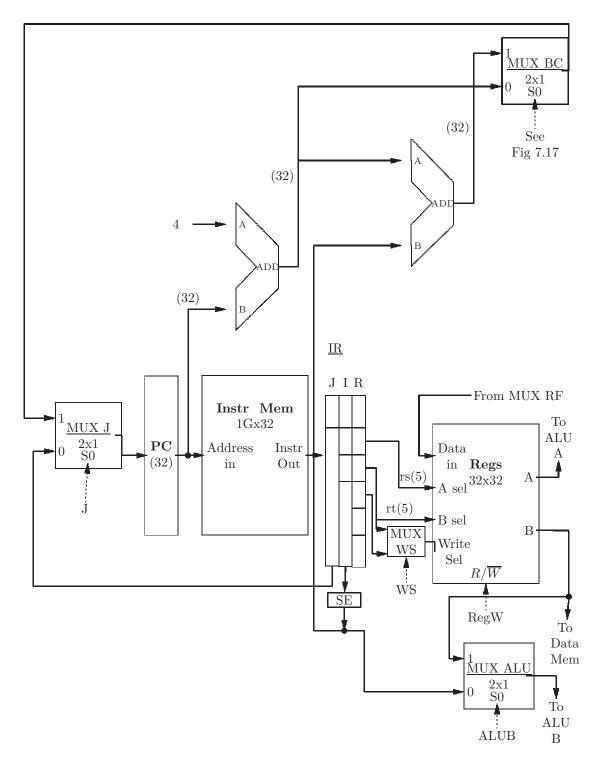

|   |     | 7.2.4  | Program Counter, Instruction Memory, and Transfer of C    | /               |

|   |     | 7.2.5  | Exercises                                                 | . 276           |

|   | 7.3 | The C  | Control Unit                                              | . 280           |

|   |     | 7.3.1  | Control Unit Output to Data Memory $R/\overline{W}$       |                 |

|   |     | 7.3.2  | Control Unit Output to Register File $R/\overline{W}$     |                 |

|   |     | 7.3.3  | Control Unit Output to ALU Operation Select - 4 bits .    |                 |

|   |     | 7.3.4  | Control Unit Output to Multiplexers                       |                 |

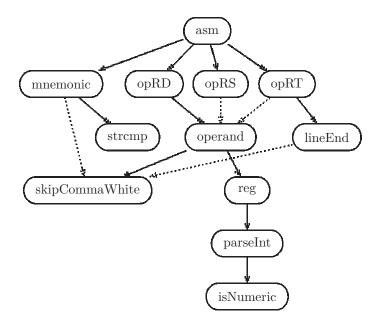

|   |     | 7.3.5  | Logic for the Control Unit                                |                 |

|   |     | 7.3.6  | Exercises                                                 |                 |

|   |     |        |                                                           |                 |

| 8 | The | Mem    | ory Hierarchy                                             | 294             |

|   | 8.1 | Introd | uction to the Memory Hierarchy                            | . 294           |

|   |     | 8.1.1  | Memory Technologies                                       | . 295           |

|   |     | 8.1.2  | Exercises                                                 | . 295           |

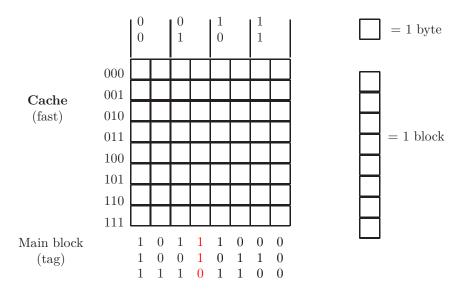

|   | 8.2 | Cache  | Memory                                                    | . 296           |

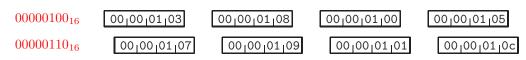

|   |     | 8.2.1  | Direct-mapped Cache                                       | . 297           |

|   |     | 8.2.2  | Associative Cache                                         |                 |

|   |     | 8.2.3  | Exercises                                                 | . 304           |

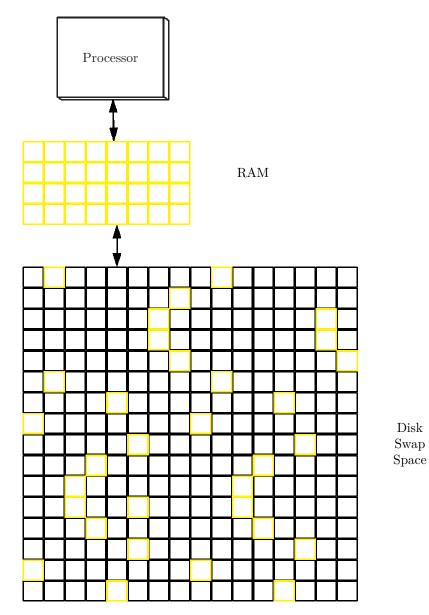

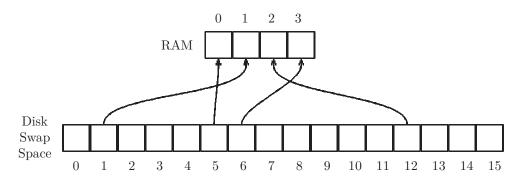

|   | 8.3 | Virtua | al Memory                                                 | . 306           |

|   |     | 8.3.1  | Exercises                                                 | . 309           |

|   | 8.4 | Locali | ty                                                        |                 |

|              |        | 8.4.1   | Data Locality Versus Instruction Locality                | 310             |

|--------------|--------|---------|----------------------------------------------------------|-----------------|

|              |        | 8.4.2   | Temporal Locality Versus Spatial Locality                | 311             |

|              |        | 8.4.3   | Exercises                                                | 313             |

| 0            | A 1+ - | matin   | A relitestures                                           | 915             |

| 9            |        |         | e Architectures                                          | 315             |

|              | 9.1    |         | ction Set Architectures                                  |                 |

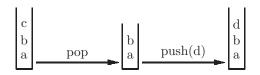

|              |        | 9.1.1   | Zero-address Architecture                                |                 |

|              |        | 9.1.2   | One-address Architecture                                 |                 |

|              |        | 9.1.3   | Two-address Architecture                                 |                 |

|              |        | 9.1.4   | Three-address Architecture                               |                 |

|              | 0.0    | 9.1.5   | Exercises                                                |                 |

|              | 9.2    |         | ssing Modes                                              |                 |

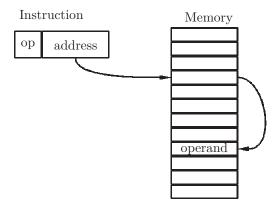

|              |        | 9.2.1   | Direct Addressing                                        |                 |

|              |        | 9.2.2   | Indirect Addressing                                      |                 |

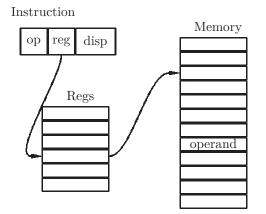

|              |        | 9.2.3   | Base Register and Displacement Addressing                |                 |

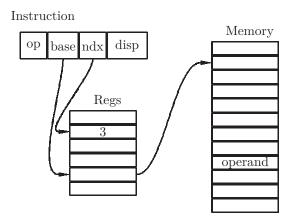

|              |        | 9.2.4   | Base Register, Index Register, and Displacement Addressi | -               |

|              |        | 9.2.5   | Exercises                                                |                 |

|              | 9.3    |         |                                                          |                 |

|              |        | 9.3.1   | Registers and instruction formats                        |                 |

|              |        | 9.3.2   | Conditional branch instructions - CB format              |                 |

|              |        | 9.3.3   | Exercises                                                | 332             |

|              | 9.4    | Intel P | Pentium                                                  | 333             |

|              |        | 9.4.1   | CPU Registers                                            | 334             |

|              |        | 9.4.2   | The Mov Instruction and Addressing Modes                 | 334             |

|              |        | 9.4.3   | Arithmetic Instructions                                  | 336             |

|              |        | 9.4.4   | Logical Instructions                                     | 339             |

|              |        | 9.4.5   | Shift/Rotate Instructions                                | 341             |

|              |        | 9.4.6   | Transfer of Control Instructions and Condition Code Flag | $	ext{ s 343 }$ |

|              | 9.5    | Examp   | ple program                                              | 345             |

|              | 9.6    | Exerci  | ses                                                      | 345             |

| Gl           | ossai  | ry      |                                                          | 348             |

| Aı           | open   | dix: M  | IARS                                                     | 357             |

|              | .1     |         | oading MARS to Your Computer                             | 357             |

|              | .2     |         | ource Files                                              |                 |

|              | .3     |         | ble Source Files                                         |                 |

|              | .4     |         | te Programs                                              |                 |

| Δ.           | nen    | div M   | IIPS Instruction Set                                     | 360             |

| - <b>-</b> ł | .5     |         | nstructions                                              |                 |

|              | .6     |         | ng Point Instructions                                    |                 |

|              | .0     | .6.1    | Floating Point Conditional Branch                        |                 |

| A            | open   | dix: P  | seudo Operations Supported by MARS                       | 369             |

viii

## CONTENTS

Appendix: ASCII Character Set

$\mathbf{372}$

CONTENTS

## Chapter 1

# Computers and Computer Programs

In driver education classes students are taught not only how to drive and the rules of the road, but they are also taught some fundamentals of the inner workings of the car - the four cycle engine, the distributor, the electrical system, etc. Strictly speaking it is not necessary to know these things in order to drive the car, but they are generally considered important enough for every driver to have a rudimentary understanding. When something fails, a mechanic may not be immediately available, and the driver who has some knowledge of what is under the hood will be better prepared to deal with the problem than the driver who is clueless.

Some computer scientists work with computer hardware (often in conjunction with software), but many work exclusively with software. Like automobile drivers they will be better prepared to deal with failures if they have some knowledge of what is 'under the hood'. In addition software developers who are hardware-savvy can produce more efficient software than those who are not.

For these reasons most computer science curricula include at least one hardware course. This book includes topics such as CPU design, datapath, the memory hierarchy, and assembly language. All of these are essential to a broad understanding of computer organization and design. A discussion of the importance of this subject to software professionals can be found in the *Kode Vicious* column by George Neville-Neil, in the March/April 2021 issue of ACM Queue.

As a prototypical example of a computer, we use the MIPS<sup>1</sup> architecture. This architecture is complex enough that it is used in some real devices, yet it is simple enough to be understood and programmed by novices.

The computer is but one example of a *digital* device. By this we mean that at its most fundamental level it stores and works with binary values - zeros and ones. There is no other value in a digital device; all other information

$<sup>^1{\</sup>rm Microprocessor}$  without Interlocked Pipeline Stages. MIPS has been used primarily in embedded systems, routers, game consoles, etc.

(numbers, keyboard characters, sound, images) are made up of sequences of zeros and ones, i.e. binary values. This is true of all digital devices - computers, tablets, phones, cameras, music players, game consoles, and electronic devices embedded in appliances, automobiles, medical equipment, etc. Each binary value is called a *bit* (binary digit).

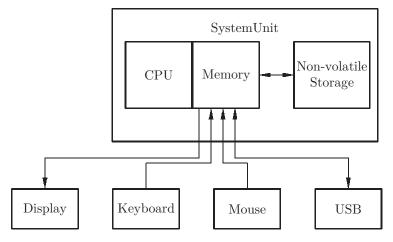

## **1.1** Hardware Components

Here we provide a simplified description of the hardware components of a typical general purpose computer, such as those which are called 'desktop' or 'laptop' computers. These are not tablet systems, nor smart phones, which have a somewhat different design. Most of the components described here reside in the *system unit* which is the box housing the desktop or laptop computer.

#### 1.1.1 Central Processing Unit

The *Central Processing Unit* (CPU) is probably the most important part of the computer. This is where computations take place, and this is where decisions are made concerning the sequence in which computations are made. The CPU consists of registers (described below), an arithmetic logic unit (ALU) capable of arithmetic and logical operations, a control unit, and other components which are connected with buses and wires.

#### Registers

The CPU registers are storage elements with fast access time. The time to access the contents of a value in the computer's memory can be over 1000 times slower than the time to access a CPU register. A register consists of a fixed number of bits, usually 32 or 64. In the MIPS architecture which we will be studying there are 32 bits in a register, and there are 32 general purpose registers. These registers can store intermediate results from arithmetic and logical computations, for which the operands must also be stored in registers. They can also be used to move information from one location in memory to another, and to store memory addresses (see the section on memory below).

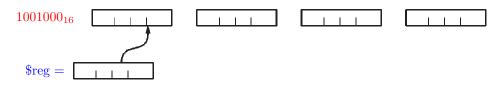

In this book we will be diagramming registers as shown in Fig 1.1 Each register is designated by a unique number: 0..31 and stores 32 bits. To save space on the page only the first 8 of 32 general registers are shown. In the MIPS architecture register 0 will always contain all zeros. The other registers in Fig 1.1 contain randomly selected values with no particular intent or purpose. We will be using these diagrams to explain the various operations which the CPU is capable of performing, by showing the contents of registers before and after the operation is performed.

| 0 | 000000000000000000000000000000000000000 |

|---|-----------------------------------------|

| 1 | 11011000010101010100010101010100        |

| 2 | 00010101000111101010101010101010101     |

| 3 | 1101000001110001001010101010101010      |

| 4 | 000000000000000111111111111111111       |

| 5 | 111111111111111100000000000000000000000 |

| 6 | 000000000000000000000000000000000000000 |

| 7 | 000000000000000000000000000000000000000 |

Figure 1.1: Possible values for 8 of the 32 CPU registers in the MIPS architecture

#### **Program Counter**

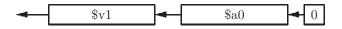

The 32 general purpose registers described above may be referred to as *pro-grammable* registers, i.e. the values which they contain can be explicitly altered at the programmer's discretion. There are other registers in the CPU which are necessary for the correct sequence of operations to take place. One such register is called the *program counter* register (PC). It contains the location (i.e. memory address) of the next instruction to be executed.

#### Datapath

The *datapath* is the name which we give to the components in the CPU which enable data to move between memory and the registers. The datapath also contains hardware which can execute fundamental arithmetic and logical operations. The following components are included in the datapath: the registers, the memory, the arithmetic/logic unit (ALU), the PC, the control unit, and the connections necessary for these components to work together.

#### 1.1.2 Memory

Closely associated with the CPU is the *memory*, also known as *main memory* or *random access memory* (RAM). The memory stores data which is needed for CPU operations. For example, if a program is working with an array of numbers, those numbers would be stored in memory, where the CPU would have immediate access to them. The instructions making up a program, coded in binary, are also stored in memory. Each memory location has a unique *address*, much like the houses on a street have unique, sequential, addresses. When the CPU needs to access a particular memory value, it uses the address of that value to access it.

The bits (binary digits) of memory are normally viewed in groups of 8 bits. Each 8-bit group is called a *byte*. In the MIPS architecture which we study in this book, each byte of memory has a unique address; we say the memory is *byte addressable*. Recalling that registers are 32 bits, every 4 bytes constitute a *full word* of memory; we say that the *word size* for the MIPS architecture is 4 bytes, or 32 bits. This means that calculations and memory access are normally 4024

4028

Figure 1.2: A portion of the MIPS memory, showing word addresses

done with 32-bit values. Fig 1.2 is a diagram of the MIPS memory structure. This diagram shows only two words of memory, each with its own address. The 32 bits in each word are shown with a space between bytes to show the 4 bytes in a word (in an actual memory there is no such space). Since there are 4 bytes in a word, and the memory is byte addressable, the word addresses increase by 4 (from 4024 to 4028 in this example).

#### **1.1.3** Peripheral Devices

#### **Peripheral Storage Devices**

The memory described in the previous section is said to be *volatile*. This means that when power is switched off, all values in memory are lost. The term volatile is taken from chemistry in which a volatile liquid is one which evaporates readily and seemingly disappears. You may have experienced a loss of data when entering text into a word processor and there was a loss of electrical power to the computer. If the document was not saved, it would be lost because it is stored in memory.

This is but one reason for the need for *peripheral* devices such as disks or flash storage systems. These devices are capable of retaining data when power is shut off. Disks can be either magnetic or optical. The fixed disk (non-removable) in your computer's system unit is typically a magnetic disk. In addition to data files it stores all the system and application software which is needed by your computer. Optical disks are removable; examples of optical disk formats are CD, CD-ROM, DVD, etc. Data written to optical disks are typically not removed, whereas data on magnetic disks are commonly over-written or removed.

Another important device for permanent storage is *flash* memory, also known as a USB stick, a USB drive, thumb drive, etc. Here the word 'drive' is a misnomer because there are no moving parts in flash memory; it is a semiconductor material which is not volatile. Most mobile devices such as tablets and phones contain a substantial amount of (non-removable) flash memory.

#### Peripheral Devices for Input and Output

The terms *input* and *output* are to be understood from the memory's perspective. Output occurs when information is transferred from memory, out to an external device. Input occurs when information is transferred in to memory, from an external device.

A printer is an example of a device which is primarily an output device. Information is sent from the computer's memory to the printer, presumably in a form which is familiar to the user.

Figure 1.3: Diagram of a computer, with peripheral devices

A monitor (or display) is also an output device. Information is constantly being sent from memory to the monitor. In most computers a section of memory is set aside specifically for this purpose, in which case the monitor is said to be *memory mapped*.

The keyboard and mouse are input devices. When the user types a key, moves the mouse, or presses a mouse button, signals are sent into the computer's memory, and the operating program is capable of responding appropriately.

Input and output can also take place through a wireless adapter and/or an ethernet port. This is useful for communication with other computers and the internet.

Fig 1.3 shows a block diagram of the components that we have described. Note that the arrows show the direction in which information flows. Data from memory flow out to the display, while data from the keyboard and mouse flow into memory. Data can flow in both directions between memory and a USB device. This gives rise to the terminology, *input* and *output* devices. The words 'input' and 'output' describe the direction of data flow, from the memory's perspective. The display, is an output device, the keyboard and mouse are input devices, and the USB port is used for both input and output.<sup>2</sup>

The non-volatile storage is typically a fixed disk, i.e. a magnetic rotating disk, which is non-removable. As flash memory<sup>3</sup> technology improves, it may replace the fixed disk as the non-volatile storage. It is not visible to the user since it is in the system unit.<sup>4</sup>

$<sup>^2\</sup>mathrm{Technically},$  the display is used for both input and output, because the display can send status signals into memory.

$<sup>^3\</sup>mathrm{Flash}$  memory is described in chapter 8

<sup>&</sup>lt;sup>4</sup>In many systems the display is also incorporated into the system unit.

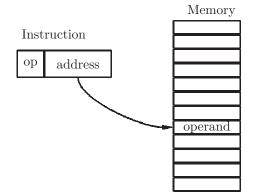

## 1.2 Machine Language

The CPU is capable of executing only the most basic and fundamental operations such as the addition of two values, the subtraction of two values, comparison of two values, etc. Furthermore these operations must be properly encoded in binary in order for the CPU to 'understand' their meaning. Such an operation is called an *instruction*. The instruction generally consists of a an operation code (for add, subtract, compare, etc) and locations of the operands (typically registers). An instruction which refers to a memory location would have to specify the address as a binary number. A sequence of binary-coded instructions in memory is called a *program*. The CPU executes the instructions of a program sequentially in the order in which they are stored in memory, unless it encounters an instruction which specifically orders it to alter that sequence. This language of binary coded instructions is usually called *machine language*; it is the only language which the CPU understands.

## 1.3 Assembly Language

Programming a computer in a binary machine language has, historically, been done; however it is obviously a tedious and error-prone way to proceed. For this reason we have developed a language called *assembly language* in which the operations are represented by plain text such as **add** and **sub**, and memory locations may be referenced with symbolic names, such as **salary** instead of a binary memory addresses. Since the CPU is not capable of executing assembly language programs, they must first be translated into machine language; this is done by software known as an *assembler*. We will be using an assembler developed at Missouri State University known as MARS <sup>5</sup>. In chapter 5 we will attempt to develop our own assembler.

## 1.4 Operating System

Computers are generally distributed with certain software built-in, known as the *operating system*. This software manages the resources available to programs as they are executed by the CPU. The functionality of the operating system includes:

- Manage access to the CPU when several programs are executing simultaneously (this is almost always the case)

- Manage access to peripheral devices such as disk, printer, keyboard, etc.

- Allow the user to manage permanent data files (create, remove, edit)

- Use non-volatile storage to expand the addressable memory, known as *virtual memory* (chapter 8)

<sup>&</sup>lt;sup>5</sup>MIPS Assembler and Runtime Simulator

Some examples of modern operating systems include:

- Windows (proprietary, licensed by Microsoft)

- MacOS (proprietary, licensed by Apple)

- Linux (open source)

- Android (open source)

- iOS (proprietary, licensed by Apple)

## 1.5 Programming Languages

The assembly language instructions correspond, for the most part, with machine language operations. In assembly language it is not possible to specify many operations in a single statement, such as a \* 32 + b \* 8. For this feature (and many others) we rely on *high-level* or *programming* languages. Examples of programming languages are Java, C++, Visual Basic, and Python. Programs written in these languages must also be translated to machine language in order to be executed; this is done by a software translator known as a *compiler*. Compilers are not covered in this book, but a free introductory textbook on compiler design can be found at cs.rowan.edu/~bergmann/books.

## 1.6 Exercises

- 1. What is a computer program?

- 2. (a) What does CPU stand for?

- (b) What are the two primary purposes of the CPU?

- 3. In the CPU where are intermediate results of calculations stored?

- 4. In the MIPS archtitecture:

- (a) How many registers are there?

- (b) What is the size (in bits) of each register?

- 5. What is the purpose of the Program Counter (PC) register?

- 6. In the MIPS architecture:

- (a) How many bits are in a byte?

- (b) How many bytes are in a word?

- (c) How many bits are in a word?

- 7. (a) If the address of a particular byte in memory is 4321, what is the address of the next byte?

- (b) If the address of a particular word in memory is 70324, what is the address of the next word?

- 8. Which of the following are *volatile* storage?

- (a) Main memory

- (b) Flash memory

- (c) Magnetic disk

- (d) Optical disk

- 9. Many game consoles utilize a *joystick* to control the game. Is the joystick considered an input or output device?

- 10. Match the words with the correct descriptions:

| 1. | Assembly Language    | (a) May contain many operations in a single statement.                 |

|----|----------------------|------------------------------------------------------------------------|

| 2. | Machine Language     | (b) Utilizes plain text to name instructions, such as 'add' and 'sub'. |

| 3. | Programming Language | (c) Primitive instructions are encoded in binary.                      |

11. Use wikipedia to find out what is meant by *open source* versus *proprietary* software. What are their relative advantages and disadvantages?

## Chapter 2

# Number Systems

In chapter 1 we introduced the notion of binary numbers. Here we generalize the notion and look at more convenient ways of describing large binary numbers. We also show how some operations on binary values can be simplified or facilitated.

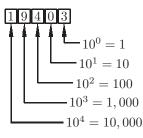

All of these number systems are based on the same positional system.<sup>1</sup> Fig 2.1 shows the decimal number 19,403. For decimal numbers the base is  $10.^{2}$  All of the number systems described here use the same principle, with different bases. We will examine the bases 2,8, and 16. Some areas of Computer Science use other bases, such as 64.

## 2.1 Base Two - Binary

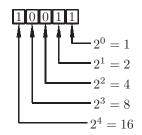

Whereas in a base ten (decimal) number each digit represents a power of 10, in base two each digit represents a power of 2, as shown in Fig 2.2 which depicts the base two representation of 19.  $19 = 1 \cdot 16 + 0 \cdot 8 + 0 \cdot 4 + 1 \cdot 2 + 1 \cdot 1 = 10011_2$ . If you add the positional values for which there is a 1 in the binary number, the

$<sup>^1 \</sup>rm Generally$  attributed to the Hindu and Arab cultures of the ninth century AD  $^2 \rm Probably$  because we have 10 fingers

Figure 2.1: The decimal representation of 19,403 (19,403 = 10,000 + 9,000 + 400 + 0 + 3)

Figure 2.2: The binary representation of 19 (19 = 16 + 2 + 1)

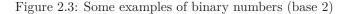

$$\begin{split} 101_2 &= 5\\ 0101_2 &= 5\\ 10101_2 &= 21\\ 10000_2 &= 16\\ 1111_2 &= 15\\ 100000000000_2 &= 4096\\ 10000000001_2 &= 4097\\ 111111111_2 &= 4095 \end{split}$$

sum is the value of the binary number. Other examples of binary numbers are shown in Fig 2.3.

### 2.1.1 Binary Arithmetic

Binary arithmetic is easy to learn; it is just like decimal arithmetic, but the only numerals permitted are 0 and 1. Simply remember that  $1_2 + 1_2 = 10_2$  and that  $1_2 + 1_2 = 11_2$ . An example showing the addition of two 8-bit numbers is shown in Fig 2.4.

Note that in any column where the result is  $10_2$ , the 0 is written and the 1 is a *carry* into the next column. In any column where the result is  $11_2$ , the

|                     | 1 1 1                     |

|---------------------|---------------------------|

| 0 0 1 0 1 0 1 1 =   | 43 0 0 1 0 1 0 1 1 = 43   |

| + 0 0 0 0 1 1 1 0 = | 14 + 0 0 0 0 1 1 1 0 = 14 |

|                     |                           |

| 0 0 1 1 1 0 0 1 =   | 57 0 0 1 1 1 0 0 1 = 57   |

| (a)                 | (b)                       |

Figure 2.4: (a) Addition of 43 + 14 in binary using 8-bit values and (b) The same operation showing *carry* bits

|   | 0 | 1 | 0 | 0 | 0  | 1 | 1 | 0 | = | 70 |

|---|---|---|---|---|----|---|---|---|---|----|

| - | 0 | 0 | 0 | 0 | 1  | 1 | 0 | 1 | = | 13 |

| - |   |   |   |   |    |   |   |   |   |    |

|   | U | U | Ŧ | Ŧ | Τ. | U | U | Ŧ | _ | 51 |

Figure 2.5: Subtraction of 70 - 13 in binary using 8-bit values

|   |   | 0 | 1 | 1 | 10 |   | 0 | 10 |   |    |

|---|---|---|---|---|----|---|---|----|---|----|

|   | 0 | 1 | Ø | Ø | Ø  | 1 | 1 | Ø  | = | 70 |

| - | 0 | 0 | 0 | 0 | 1  | 1 | 0 | 1  | = | 13 |

|   | 0 | 0 | 1 | 1 | 1  | 0 | 0 | 1  | = | 57 |

Figure 2.6: Subtraction of 70 - 13 in binary using 8-bit values and showing a *borrow* from the neighboring column

(low-order) 1 is written and the (high-order) 1 is a carry into the next column.

Subtraction is similar to addition. When attempting to subtract  $0_2 - 1_2$  we will need to *borrow* a 1 from the its (high-order) neighbor. If that neighbor is a 0, it will become 1 by borrowing from *its* neighbor, and so on. An example of a binary subtraction is shown in Fig 2.5 in which we subtract 70 - 13. Fig 2.6 shows the same operation, with the borrow digits at the top. In our example we are subtracting a small number from a larger number, ensuring that we get a positive result. If we were to subtract a large number from a smaller number, the result would be negative. This implies that we need a way to represent negative numbers, which is described in the section on Twos Complement Representation.

#### 2.1.2 Exercises

- 1. Show each of the following numbers as an 8-bit binary value: 15, 3, 0, 64, 63, 127

- 2. Show the following numbers in binary using only as many bits as are needed: 15, 3, 0, 128, 255, 256

- 3. Show the following binary numbers in decimal: 0101, 0111, 0111111, 01010101, 0100000

- 4. Show how to do the following operations in binary, using 8-bit words (show the carry bits for additions as shown in Fig 2.4(b) and the borrows for subtractions as shown in Fig 2.6): 12+3, 64+64, 64+63, 63+63, 12-4, 17-3, 128-127

- 5. Read parts (a) and (b) aloud so that they make sense.

- (a) There are 10 kinds of people in the world: those who know binary and those who do not.

Figure 2.7: The octal representation of 543 (543 = 512 + 24 + 7)

$\begin{array}{l} 23_8 = 19\\ 205_8 = 69\\ 1000_8 = 512\\ 3012_8 = 1546\\ 1001_8 = 513\\ 777_8 = 511 \end{array}$

Figure 2.8: Some examples of octal numbers (base 8)

- (b) There are 10 kinds of people in the world: those who know base 3, those who do not know base 3, and those who do not know what I'm talking about.

- (c) Make up a statement similar to the ones in parts (a) and (b) above, using a base in the range [4..9].

- 6. Show how to count from 0 to 31 using only the fingers on one hand (try not to offend anyone when you get to 4).

## 2.2 Base 8 - Octal

We wish to explore other number bases, primarily because they can be used as a *shorthand* for binary numbers. In this section we look at base 8, or octal, numbers.

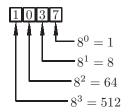

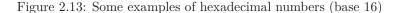

In base 8 the numerals are 0..7, and each position represents a power of 8, as shown in Fig 2.7. We multiply the numeral in each position with the number represented by the position and add the results.  $543 = 1.512 + 0.64 + 3.8 + 7.1 = 1037_8$ .

Other examples of octal numbers are shown in Fig 2.8 in which numbers shown without subscripts are assumed to be base ten.

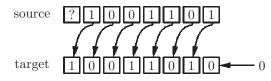

Why are we concerned with base 8? The best reason is that it provides us with a shorthand for binary numbers. Each octal digit represents 3 binary digits, as shown in Fig 2.9.

This means that we have a convenient way to represent long strings of bits - simply group them into groups of 3 bits, and represent each 3-bit group with an octal digit, as shown in Fig 2.10. Notice the last line in Fig 2.10 in which

| octal | binary |

|-------|--------|

| 0     | 000    |

| 1     | 001    |

| 2     | 010    |

| 3     | 011    |

| 4     | 100    |

| 5     | 101    |

| 6     | 110    |

| 7     | 111    |

Figure 2.9: Each octal digit represents 3 bits

| binary           | groups of 3                       | octal      |

|------------------|-----------------------------------|------------|

| 010101           | 010 101                           | $25_{8}$   |

| 111011001        | $111\ 011\ 001$                   | $731_{8}$  |

| 1111111111111    | 111 111 111 111                   | $7777_{8}$ |

| 1011101011000111 | $1 \ 011 \ 101 \ 011 \ 000 \ 111$ | $135307_8$ |

Figure 2.10: Each octal digit represents 3 bits

the number of bits provided is 16 (not a multiple of 3). This means we have one bit 'left over'. It must be the left-most bit, not the right-most bit, in order that the octal result represents the same number as the given binary value.

Conversely, we have a more common situation: we are given the octal representation of an n-bit field. If n is not a multiple of 3, the high order octal digit does not represent 3 bits. For example, if we are describing a 10-bit field in octal as  $1234_8$ , then the 10-bit field is 1 010 011 100 = 1010011100. The high order (leftmost) octal digit represents just one bit. Another example, if describing a 5-bit field as  $32_8$ , the 5-bit field must be 11 010 = 11010. In this case the high order octal digit represents just 2 bits. It will be important to remember this when dealing with the MIPS architecture in which the word size is 32 bits (not a multiple of 3), and many of the field widths in MIPS instructions are not multiples of 3.

### 2.2.1 Exercises

- 1. Show each of the following decimal numbers in base 8, using only as many octal digits as are necessary: 7, 9, 23, 100, 511, 512

- 2. Show each of the following octal numbers in decimal (base 10):  $12_8,\,32_8,\,77_8,\,777_8,\,1000_8,\,1010_8$

- 3. Show each of the following binary values in base 8, using only as many octal digits as are necessary: 111<sub>2</sub>, 110<sub>2</sub>, 100000000<sub>2</sub>, 100000001<sub>2</sub>, 11111111<sub>2</sub>, 10101011<sub>2</sub>, 1111111<sub>2</sub>

Hint: There is no need to convert to decimal.

| hexadecimal | binary | decimal |

|-------------|--------|---------|

| 0           | 0000   | 0       |

| 1           | 0001   | 1       |

| 2           | 0010   | 2       |

| 3           | 0011   | 3       |

| 4           | 0100   | 4       |

| 5           | 0101   | 5       |

| 6           | 0110   | 6       |

| 7           | 0111   | 7       |

| 8           | 1000   | 8       |

| 9           | 1001   | 9       |

| a           | 1010   | 10      |

| b           | 1011   | 11      |

| с           | 1100   | 12      |

| d           | 1101   | 13      |

| е           | 1110   | 14      |

| f           | 1111   | 15      |

Figure 2.11: Base 16: Each hexadecimal digit represents 4 bits. The 16 hex numerals have values ranging from 0 to 15.

4. Show each of the following octal values in binary (base 2):  $10_8,\,37_8,\,73_8,\,234_8,\,7150_8$

Hint: There is no need to convert to decimal.

- 5. An 8-bit field is storing the value 10101011<sub>2</sub>. Show the 8-bit field in octal, using no more digits than are necessary.

- 6. What is the largest (decimal) value that can be represented with 4 octal digits?

## 2.3 Base 16 - Hexadecimal

In this section we look at base 16, or hexadecimal, numbers which are more useful and more commonly used than octal numbers as a shorthand for binary.

Recall that in base two there are only two numerals: 0 and 1. In base 8 there are 8 numerals: 0,1,2,3,4,5,6,7. In base 10 there are 10 numerals: 0,1,2,3,4,5,6,7,8,9. This implies that in base 16 we will need 16 numerals, though the character set provides only 10 numeric characters; we will have to supplement these numeric characters with 6 more characters to represent the decimal values 10, 11, 12, 13, 14, 15. We use the first 6 letters of the alphabet for this purpose, as shown in Fig 2.11.

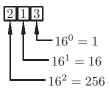

Fig 2.12 shows how the decimal number 541 can be represented in hexadecimal.  $541 = 2 \cdot 16^2 + 1 \cdot 16^1 + 3 = 213_{16}$ .

Other examples of hexadecimal numbers are shown in Fig 2.13.

Figure 2.12: The hexadecimal (base 16) representation of 541 (541 = 512 + 16 + 3)

$\begin{array}{l} a3_{16} = 10 \cdot 16 + 3 = 163 \\ 20d_{16} = 2 \cdot 16^2 + 0 \cdot 16 + 13 = 512 + 0 + 13 = 525 \\ 1000_{16} = 1 \cdot 16^3 + 0 \cdot 16^2 + 0 \cdot 16 + 0 = 4096 \\ 3012_{16} = 3 \cdot 16^3 + 0 \cdot 16^2 + 1 \cdot 16 + 2 = 12288 + 16 + 2 = 12306 \\ 1001_{16} = 1 \cdot 16^3 + 0 \cdot 16^2 + 0 \cdot 16 + 1 = 4097 \\ ff_{16} = 15 \cdot 16^2 + 15 \cdot 16 + 15 = 4095 \end{array}$

Note that each hexadecimal digit represents 4 bits, thus providing a somewhat more efficient representation for long bit strings. Fig 2.14 shows some examples of bit strings which can be represented much more easily in hexadecimal. Note in the last line of Fig 2.14 that the number of bits (19) is not a multiple of 4. We have 3 bits left over. As in the case with octal numbers, these left over bits must be the high order (leftmost) bits, in order for the number represented by the hex digits to be equal to the number represented by the given binary digits.

We will often show hexadecimal values with a subscript of 'x' instead of 16 to indicate base 16.  $321_x = 321_{16} = 801$ . When using the MARS software, there are no subscripts, so base 16 constants will be designated with a prefix of '0x'.  $0x321 = 321_{16} = 801$ . The student may often see numbers written without any base indicated. These are usually intended to be base 10, but at times the base is evident from the context. For example, the 6-bit opcode is 101001 is obviously binary, and the result in register 2 is 4a56bf0f is obviously base 16.

| binary              | groups of 4                   | hexadecimal  |

|---------------------|-------------------------------|--------------|

| 01010111            | 0101 0111                     | $57_{16}$    |

| 111010110001        | $1110\ 1011\ 0001$            | $eb1_{16}$   |

| 111111111111111111  | 1111 1111 1111 1111           | $fff_{16}$   |

| 1011011101011001111 | $101\ 1011\ 1010\ 1100\ 1111$ | $5bacf_{16}$ |

Figure 2.14: Each hexadecimal digit represents 4 bits

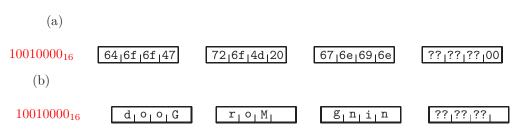

#### 2.3.1 Hexadecimal Values in the MIPS Architecture

In the MIPS architecture which we are examining, the word size is 32 bits, but often words are broken into groups of bits called *fields*. When we describe the contents of a word (whether it be a register or a word in memory) we will generally use hexadecimal as a shorthand for the actual binary digits in a word.

For example, a word could contain the 32 bits

10010110111100011010001100011000

However it is easier to describe this word in hexadecimal than in binary, and it is easier for someone to grasp this word in hexadecimal than in binary. Can you look at the 32 bit word above and memorize it? We will now convert it to hexadecimal, first by grouping the 32 bits into fields of 4 bits:

1001 0110 1111 0001 1010 0011 0001 1000

It is then easy to convert each 4-bit field to a hexadecimal digit: 96f1a318

You will probably have more success memorizing the word in this form.

In later chapters we will be examining the fields in a MIPS instruction. In some instructions the bits are grouped in fields of size 6,5,5,5,5,6. Thus an instruction, in binary, could be:

$101001 \ 10001 \ 00000 \ 11111 \ 01000 \ 000111$

To describe each field separately we would need two hex digits for each field, whether it represents 5 or 6 bits (for a 6-bit field, the high order hex digit represents two bits, and for a 5-bit field the high order digit represents just one bit):

29 11 00 1f 08 07

To describe the entire word in hexadecimal, we need to regroup the 32 bits into fields of 4 bits each:

$\begin{array}{c} 1010.01 \ 10.001 \ 0.0000.1111.1 \ 010.00 \ 00.0111 \\ 1010 \ 0110 \ 0010 \ 0000 \ 1111 \ 1010 \ 0000 \ 0111 \end{array}$

This can now be shown in hexadecimal by substituting the correct hex digit for each group of 4 bits:

a620 fa07

#### 2.3.2 Exercises

- 1. Show the following decimal values in hexadecimal (base 16): 13, 25, 170, 4095, 4096

- 2. Show the following hexadecimal values in decimal (base 10):  $12_{16}$ ,  $20_{16}$ ,  $2e_{16}$ ,  $ff_{16}$ ,  $100_{16}$ ,  $abc_{16}$ ,  $ff_{16}$ ,  $1000_{16}$

- 3. Convert the following hexadecimal values to binary:  $92_{16}$ ,  $b9_{16}$ ,  $2bf_{16}$ ,  $fff_{16}$ ,  $1000_{16}$ ,  $ffff_{16}$ Hint. Do not convert to decimal. Do not multiply

Hint: Do not convert to decimal. Do not multiply.

- 4. Convert the following binary values to hexadecimal:  $10110001_2$ ,  $1111101_2$ ,  $000100111110_2$ ,  $111111111_2$ ,  $111111111_2$ ,  $111111111_2$ ,  $111111111_2$  $11111111_2$ Hint: Do not convert to decimal.

- 5. A 15-bit field is storing the value 101111101111100<sub>2</sub>. Show this field in hexadecimal, using no more digits than necessary.

- 6. What is the largest value (in decimal) which can be represented with 4 hexadecimal digits?

- 7. A MIPS register contains the value 0xab3c401f. Show the 32 bits stored in that register.

- 8. A MIPS instruction with 6 fields (in hexadecimal) is 13 13 0f 1d 03 3a.

- (a) Show that instruction in binary (32 bits).

- (b) Show that instruction as a full word, using 8 hexadecimal digits.

## 2.4 Twos Complement Representation

We have seen that it is possible to represent non-negative whole numbers in binary (base 2), but we have not said anything about representing negative whole numbers. Recall that there are no minus signs ('-') in the computer's memory - only zeros and ones.

| Number | binary |

|--------|--------|

| +7     | 0111   |

| +6     | 0110   |

| +5     | 0101   |

| +4     | 0100   |

| +3     | 0011   |

| +2     | 0010   |

| +1     | 0001   |

| 0      | 0000   |

| -1     | 1111   |

| -2     | 1110   |

| -3     | 1101   |

| -4     | 1100   |

| -5     | 1011   |

| -6     | 1010   |

| -7     | 1001   |

| -8     | 1000   |

Over the years various schemes have been used to represent negative whole numbers. At the present time almost every computer architecture uses a representation scheme called *twos complement* representation. With this scheme it becomes possible to add and subtract whole numbers without worrying about whether they are positive or negative; we always get the correct result.

To describe twos complement in an easy to understand way, we will work with a 4-bit word instead of a 32-bit word, but the same concepts will apply to a 32-bit word. Fig 2.15 shows the positive and negative values assigned to a 4-bit word. Note that:

- Zero is neither positive nor negative

- The largest positive value is 0111 = +7

- The smallest negative value is 1000 = -8

- There are more negative numbers than positive

- Every negative number begins with a 1 in the highorder (leftmost) bit

Figure 2.15: Twos complement representation of positive and negative whole numbers, for a 4-bit word • All ones represents -1 (for any word size).

It should be clear why the positive numbers are as shown in Fig 2.15, but the negative numbers may require some explanation. Think back to the days when a car's

odometer<sup>3</sup> was mechanically connected to the wheels, so that when the car backs up, the number on the odometer decreases. Now imagine that a brand new car, with an odometer reading of 000000 backs up 1 mile. What would you see on the odometer? Most likely 999999, which is equivalent to -1. For this reason -1 is represented in twos complement by all 1's.

Now try adding -1 to some other value, in binary (discard the bit carried out from the high order position):

```

0110 = +6

+ 1111 = -1

-----

0101 = +5

```

Students often ask, given a binary value, how do you know whether it is intended to be twos complement representation? For example, does the binary value 1100 represent 12 or -4? The answer is that given no other information about this binary value, it is impossible to know what it is supposed to represent. If you are told that it is two's complement representation, then you know it represents -4. But if you are told that it is *unsigned*, then you know it represents 12. You will see this concept again when we look at the instructions in the MIPS architecture. There are two add instructions, one of which is called add unsigned. The first add instruction assumes twos complement representation, and the add unsigned instruction assumes all values are non-negative.

How can we negate a value in twos complement representation? Here are three fairly easy algorithms for negating (or complementing) a number in binary:

- Subtract from 0. 0 x = -x

- 1. Change all zeros to ones, and change all ones to zeros (this is called the *ones complement*).

- $2. \ \mathrm{Add} \ 1$

- Scan the bits from right to left.

- 1. As you scan, copy the low-order zeros

- 2. Copy the first 1 digit

- 3. Complement all remaining digits

As an example, we wish to negate (i.e. complement) the 4-bit binary value 0100 = +4. Using the first algorithm, we subtract from 0:

<sup>&</sup>lt;sup>3</sup>An odometer measures a car's mileage; don't confuse it with a speedometer

When attempting to borrow from the high-order bit, we assume there is an extra 1 at the high-order end of the number, if needed.

If we negate that result, we should obtain the value we started with (-x = x).

0000 = 0 - 1100 = -4 ------0100 = +4

We will now negate the same value, +4 = 0100, using the second algorithm. First, form the ones complement:

## 1011 Next, add 1: 1011 + 0001 = +1

1011 + 0001 = +1 -----1100 = -4

Using the same algorithm to negate that result, we should obtain +4 = 0100. First, form the ones complement of 1100, to obtain 0011. Then add 1:

```

0011

+ 0001 = +1

-----

0100 = +4

```

We will now negate the same value, +4 = 0100, using the third algorithm. Scanning from right to left we copy the low-order zeros:

0100

We then copy the first 1 digit:

```

0100

100

```

Finally we complement the remaining digits:

0100 1100 = -4

Using the same algorithm to negate that result, we should obtain +4 = 0100. Scanning from right to left we copy the low-order zeros: 1100 00

We then copy the first 1 digit:

1100 100

Finally we complement the remaining digits:

1100 0100 = +4

In summary, we have seen that negative as well as positive numbers can be represented using the twos complement representation. This scheme allows for easy implementation of addition and subtraction, and it is used by virually every chip maker in the world.

### 2.4.1 Exercises

- 1. Show the following numbers using 8-bit twos complement representation: +6, -1, -2, -6, +22, -15, +127, -127, -128

- 2. (a) What are the largest and smallest numbers which can be represented using 8-bit twos complement representation?

- (b) What are the largest and smallest numbers which can be represented using an n-bit twos complement representation?

- 3. Show each of the following in twos complement representation, using only as many bits as are necessary: 15, 23, -15, -23, 2, 1, 0, -1, -2, 511, 512, -512

Hint: A twos complement number is negative if and only if the high order bit is 1.

4. Show the decimal value of each of the following assuming (a) unsigned (b) twos complement representation:

$\begin{array}{c} 0111_2 \\ 1111_2 \\ 0101_2 \\ 1010_2 \\ 011_2 \\ 11_2 \\ 1111111_2 \\ 11111110_2 \\ 11010101_2 \\ 10_2 \\ 1_2 \\ 01_2 \end{array}$

20

#### 2.5. POWERS OF TWO

5. Use any of the three algorithms given to negate each of the following, showing the solution in binary (binary numbers are twos complement representation).

+75-76 +15 1111<sub>2</sub> 01000<sub>2</sub> 10001<sub>2</sub> 1111<sub>2</sub>

- 6. A java int is a 32-bit whole number in twos complement representation. The class variable Integer.MAX\_VALUE is the largest possible int, and the class variable Integer.MIN\_VALUE is the smallest possible int.

- (a) What is Integer.MAX\_VALUE + Integer.MIN\_VALUE?

- (b) What is Integer.MIN\_VALUE Integer.MAX\_VALUE?

- (c) What is Integer.MAX\_VALUE + Integer.MAX\_VALUE?

- (d) What is Integer.MIN\_VALUE + Integer.MIN\_VALUE?

Hint: See Fig 2.15. Use a java compiler to check your solutions if you are not sure.

## 2.5 Powers of Two

Computers are binary machines; consequently it is important that we be familiar with the powers of two. These numbers will also be cropping up in other areas of computer science, such as analysis of algorithms. In this section we will see how to find any power of 2 up to  $2^{49}$ ; moreover we will be able to do this mentally, without help from pencil, paper, nor digital device. We will also see some easy ways of doing arithmetic with powers of two. Fig 2.16 shows the powers of two up to  $2^{10} = 1024$ . Students should memorize these numbers; this will make it easy to do important calculations mentally.

Next we introduce some standard notation for large powers of two.<sup>4</sup>  $2^{10} = 1024 = 1K$

1K is the same as 1024; in this book 1K always represents 1024, and never 1000. 1K is simply a number and could be used to specify a quantity of memory (1K bytes or 1K words or 1K bits) as well as anything else (1K rabbits). Using this notation we have larger powers of two:

$\begin{array}{l} 2^{11} = 2 \cdot 2^{10} = 2K \\ 2^{12} = 4 \cdot 2^{10} = 4K \end{array}$

<sup>&</sup>lt;sup>4</sup>We observe the convention that capital letters are used for powers of 2, and lower case letters for powers of ten. Thus  $1K = 2^{10} = 1024$  but  $1k = 10^3 = 1000$ .

| n  | $2^n$ |

|----|-------|

| 0  | 1     |

| 1  | 2     |

| 2  | 4     |

| 3  | 8     |

| 4  | 16    |

| 5  | 32    |

| 6  | 64    |

| 7  | 128   |

| 8  | 256   |

| 9  | 512   |

| 10 | 1024  |

Figure 2.16: The powers of two

$$2^{13} = 8 \cdot 2^{10} = 8K$$

$$2^{19} = 512 \cdot 2^{10} = 512K$$

We have standard notation for larger powers of two.  $2^{20} = 2^{10} \cdot 2^{10} = 1024 \cdot 1K = 1M$ Some examples are:  $2^{21} = 2 \cdot 2^{20} = 2M$   $2^{22} = 4 \cdot 2^{20} = 4M$   $2^{23} = 8 \cdot 2^{20} = 8M$  $2^{29} = 512 \cdot 2^{20} = 512M$

| n  | $2^n$         |

|----|---------------|

| 3  | 8             |

| 13 | 8K            |

| 17 | 128K          |

| 21 | 2M            |

| 25 | 32M           |

| 32 | $4\mathrm{G}$ |

| 38 | 256G          |

| 40 | $1\mathrm{T}$ |

| 49 | 512T          |

And yet larger powers of two:  $2^{30} = 2^{10} \cdot 2^{20} = 1024 \cdot 1M = 1G$ Some examples are:  $2^{31} = 2 \cdot 2^{30} = 2G$   $2^{32} = 4 \cdot 2^{30} = 4G$   $2^{33} = 8 \cdot 2^{30} = 8G$  $2^{39} = 512 \cdot 2^{30} = 512G$

Using the notation,  $2^{40} = 2^{10} \cdot 2^{30} = 1024 \cdot 1G = 1T$ we can now easily describe any power of 2 up to  $2^{49}$

Figure 2.17: Examples of large powers of 2

A few examples are shown in Fig 2.17. How are these values obtained? The letter - K,M,G, or T - is determined by the the first digit in the exponent of 2. 1=K 2=M 3=G 4=T. The number before the letter is two raised to the power of the second digit.  $2^0 = 1$   $2^1 = 2$   $2^2 = 4$   $2^3 = 8$  (these are shown in Fig 2.16, and you've memorized them).

The next time you are at a party with friends you can impress people by announcing that you know all the powers of two, up to  $2^{49}$ !

## 2.5.1 Arithmetic With Powers of Two

You may recall the following properties of exponents from your math classes:

- $x^y \cdot x^z = x^{y+z}$

- $x^y/x^z = x^{y-z}$

- $x^{y^z} = x^{y \cdot z}$

These properties will make arithmetic with powers of two much easier:

- $2^2 \cdot 2^3 = 2^{2+3} = 2^5 = 32$

- $2^9/2^3 = 2^{9-3} = 2^6 = 64$

- $2^{2^3} = 2^{2 \cdot 3} = 2^6 = 64$

- $1K \cdot 4K = 2^{10} \cdot 2^{12} = 2^{10+12} = 2^{22} = 4M$

- $64K \cdot 32K = 2^{16} \cdot 2^{15} = 2^{16+15} = 2^{31} = 2G$

- $8G/32K = 2^{33}/2^{15} = 2^{33-15} = 2^{18} = 256K$

- $2K^4 = (2^{11})^4 = 2^{11 \cdot 4} = 2^{44} = 16T$

We will be working extensively with powers of two in chapter 8 and will find it much easier using what we have learned here.

### 2.5.2 Exercises

1. Complete the following table, using the KMGT notation introduced in this section:

| n  | $2^n$         |

|----|---------------|

| 3  |               |

| 7  |               |

| 11 |               |

| 15 |               |

| 20 |               |

| 24 |               |

| 36 |               |

| 48 |               |

|    | 16            |

|    | 512           |

|    | 8K            |

|    | 128K          |

|    | 1M            |

|    | 64M           |

|    | $4\mathrm{G}$ |

|    | 32G           |

|    | 32T           |

|    | 512T          |

- 2. Evaluate each of the following:

- (a) 4K \* 32K

- (b) 16M \* 16M

- (c) 32M \* 64G / 2T

- (d) 16T \* 32G \* 128M / 4T / 8T

- (e)  $(32K)^3$

Hint: See the identities in this section, and use powers of two.

- 3. Use the definitions provided in this section.

- (a) If there are 128K protozoa in a liter of pond water, and there are 4M liters of water in the pond, how many protozoa are in the pond?

- (b) If a ROM (read-only memory) consists of 4G bits, and there are 8 hits in a byte, how many bytes are in the ROM?

# Chapter 3

# Assembly Language for MIPS

In chapter 1 we described the fundamental components of a computer, including the CPU. We also described the notion of a program as a sequence of binary coded instructions stored in the computer's memory. We also introduced the notion of *assembly* language, in which we can use *mnemonics* and symbolic names rather than binary codes. Software known as an *assembler* is then needed to translate programs written in assembly language into equivalent machine language programs. In this chapter we deal exclusively with assembly language for a particular CPU known as MIPS.

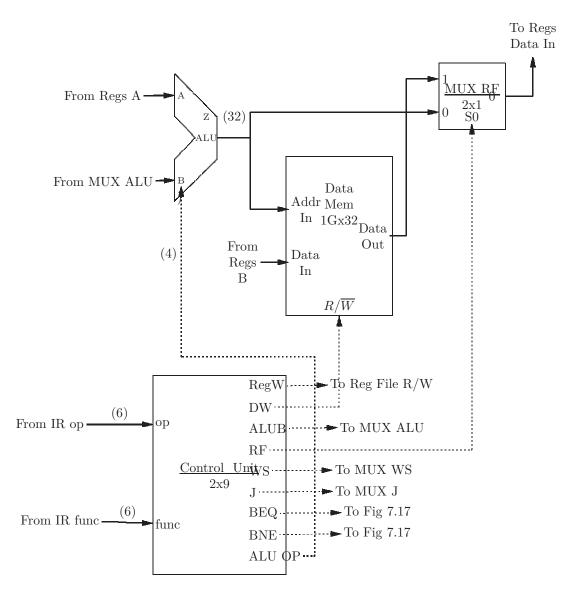

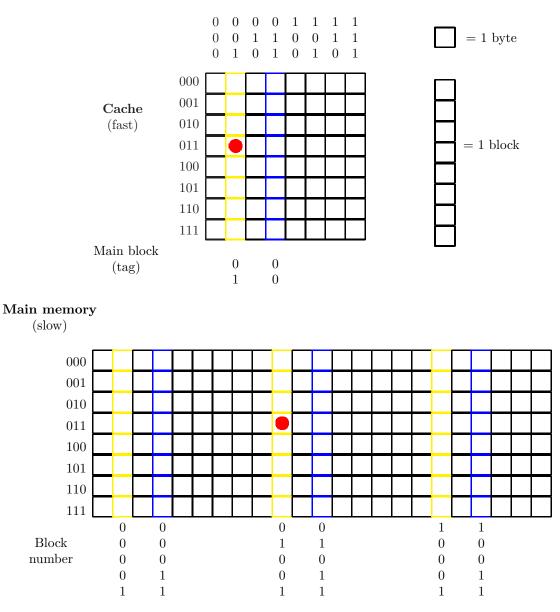

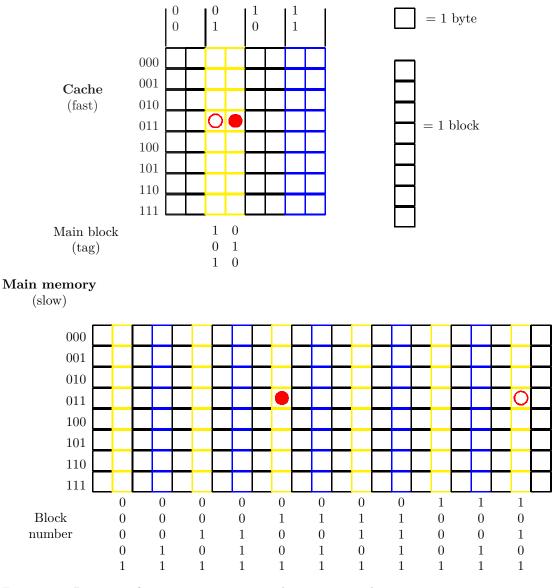

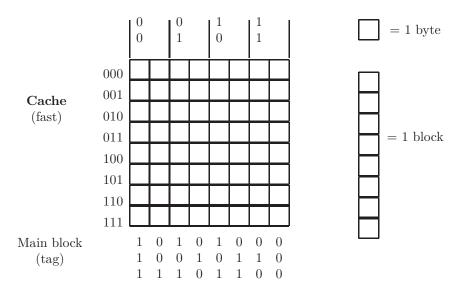

# 3.1 Registers and Register Names